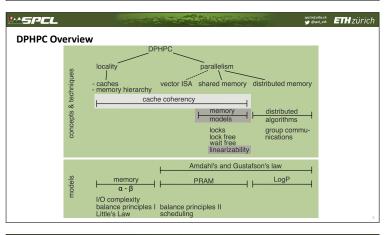

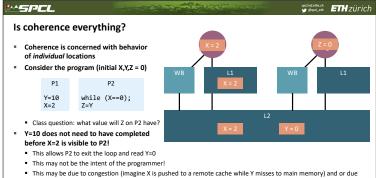

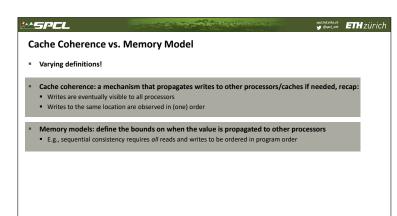

ETH zürich **Review of last lecture** Architecture case studies Memory performance is often the bottleneck Parallelism grows with compute performance · Caching is important Several issues to address for parallel systems Cache Coherence Hardware support to aid programmers Two guarantees: Write propagation (updates are eventually visible to all readers) Write serialization (writes to the same location are observed in global order) Two major mechanisms: Snooping Directory-based Protocols: MESI (MOESI, MESIF)

Bonus class question: what happens when Y and X are on the same cache line (assume simple MESI and

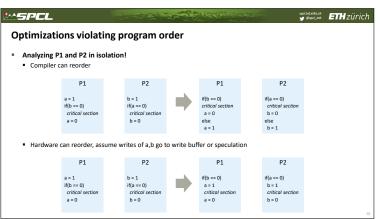

to write buffering, or

no write buffer)?

Good read: McKenney: "Memory Barriers: a Hardware View for Software Hackers"

## x86 Memory model: TLO + CC ■ Total lock order (TLO) ■ Instructions with "lock" prefix enforce total order across all processors ■ Implicit locking: xchg (locked compare and exchange) ■ Causal consistency (CC) ■ Write visibility is transitive ■ Eight principles ■ After some revisions ③

The Eight x86 Principles

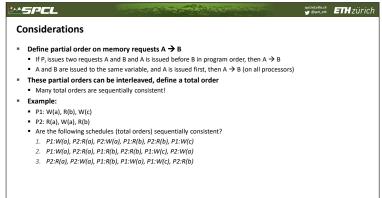

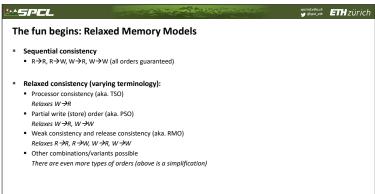

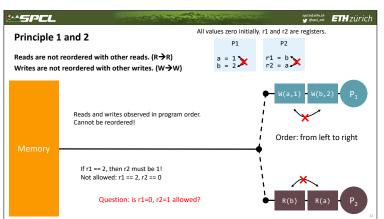

1. "Reads are not reordered with other reads." (R→R)

2. "Writes are not reordered with other writes." (W→W)

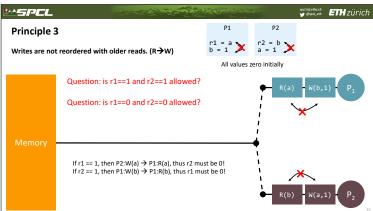

3. "Writes are not reordered with older reads." (R→W)

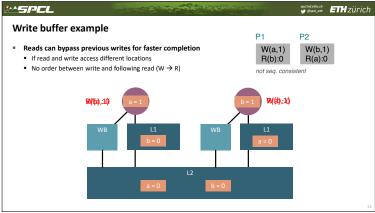

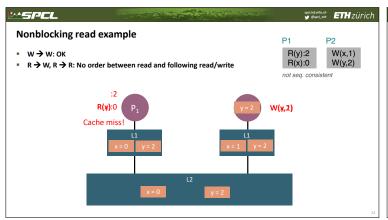

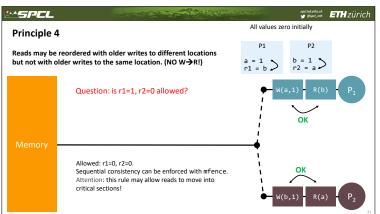

4. "Reads may be reordered with older writes to different locations but not with older writes to the same location." (NO W→R!)

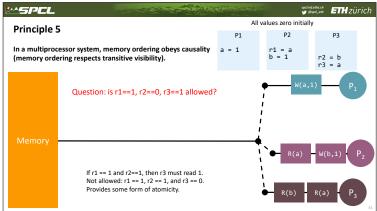

5. "In a multiprocessor system, memory ordering obeys causality." (memory ordering respects transitive visibility)

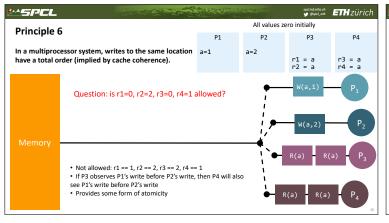

6. "In a multiprocessor system, writes to the same location have a total order." (implied by cache coherence)

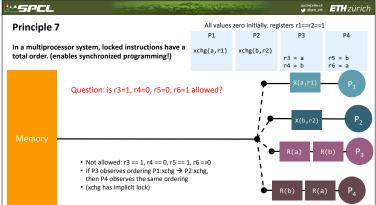

7. "In a multiprocessor system, locked instructions have a total order." (enables synchronized programming!)

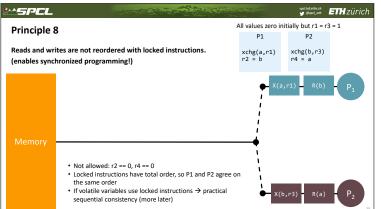

8. "Reads and writes are not reordered with locked instructions. " (enables synchronized programming!)

wer RMA systems: A. Dan, P. Lam, TH, A. Vechev: Modeling and Analysis of Remote Memory Access Programming, ACM OOPSLA'16

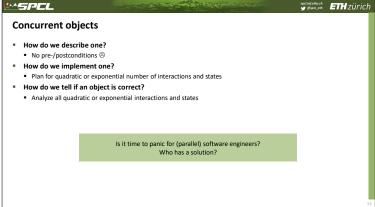

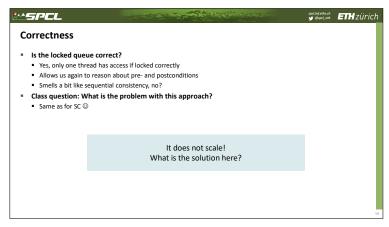

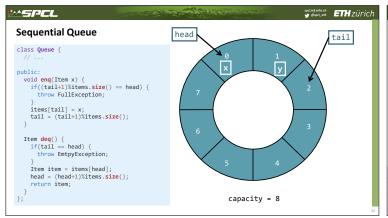

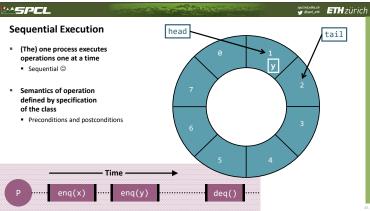

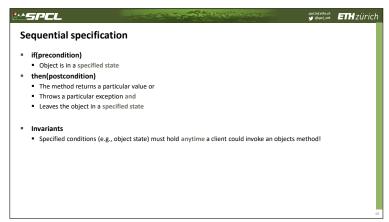

Advantages of sequential specification

State between method calls is defined

Enables reasoning about objects

Interactions between methods captured by side effects on object state

Enables reasoning about each method in isolation

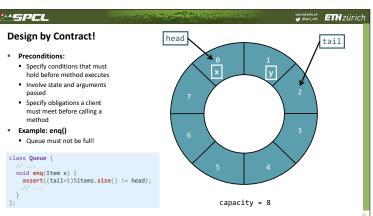

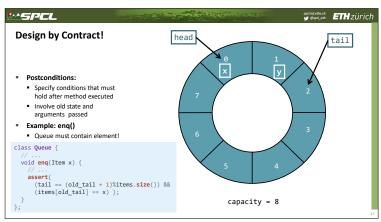

Contracts for each method

Local state changes global state

Adding new methods

Only reason about state changes that the new method causes

If invariants are kept: no need to check old methods

Modularity!