# Multiple signals

ETH zürich

- If multiple signals of the same type are to be delivered, Unix will discard all but one.

- If signals of different types are to be delivered, Unix will deliver them in any order.

- Serious concurrency problem: How to make sense of this?

5

# **ETH** zürich A better signal () POSIX sigaction () New action for signal signo #include <signal.h> Previous action int sigaction(int signo, is returned const struct sigaction \*act, struct sigaction \*oldact); Signal handler struct sigaction { void (\*sa handler)(int); Signals to be blocked in this sigset t sa mask; handler (cf., fd\_set) int sa flags; void (\*sa\_sigaction)(int, siginfo\_t \*, void \*); }; More sophisticated signal handler (depending on flags)

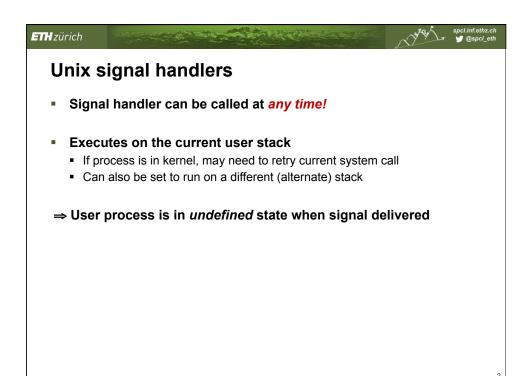

# Signals as upcalls

- Particularly specialized (and complex) form of Upcall

- Kernel RPC to user process

- Other OSes use upcalls much more heavily

- Including Barrelfish

- "Scheduler Activations": dispatch every process using an upcall instead of return

- Very important structuring concept for systems!

7

ETH zürich spcl.inf.ethz.ch

y @spcl\_eth

# **Our Small Quiz**

- True or false (raise hand)

- Mutual exclusion on a multicore can be achieved by disabling interrupts

- Test and set can be used to achieve mutual exclusion

- Test and set is more powerful than compare and swap

- The CPU retries load-linked/store conditional instructions after a conflict

- The best spinning time is 2x the context switch time

- Priority inheritance can prevent priority inversion

- The receiver never blocks in asynchronous IPC

- The sender blocks in synchronous IPC if the receiver is not ready

- A pipe file descriptor can be sent to a different process

- Pipes do not guarantee ordering

- Named pipes in Unix behave like files

- A process can catch all signals with handlers

- Signals always trigger actions at the signaled process

- One can implement a user-level tasking library using signals

- Signals of the same type are buffered in the kernel

8

# Firminology Physical address: address as seen by the memory unit Virtual or Logical address: address issued by the processor Loads Stores Instruction fetches Possible others (e.g., TLB fills)...

# **Memory management**

**ETH** zürich

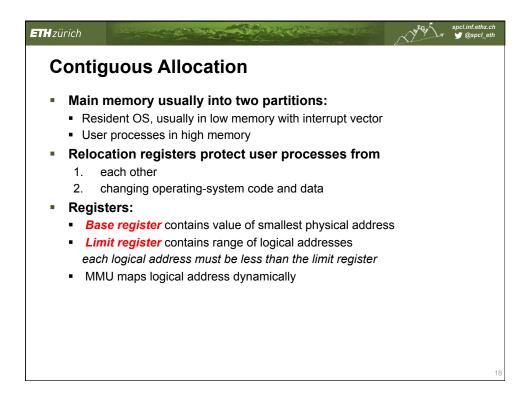

- 1. Allocating physical addresses to applications

- 2. Managing the name translation of virtual addresses to physical addresses

- 3. Performing access control on memory access

- Functions 2 & 3 usually involve the hardware Memory Management Unit (MMU)

13

# Simple scheme: partitioned memory

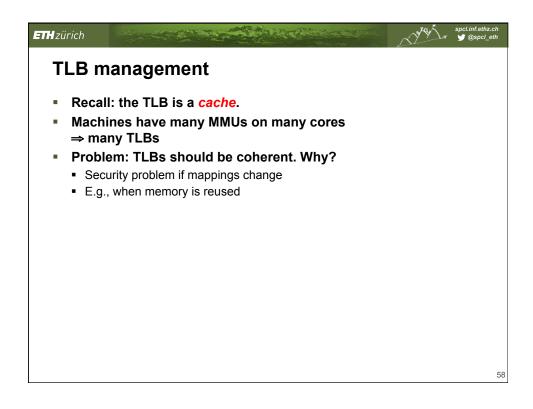

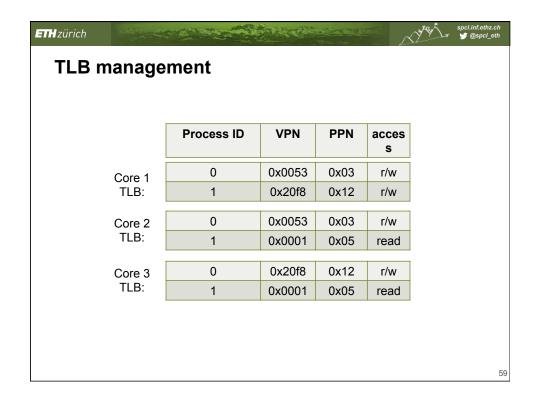

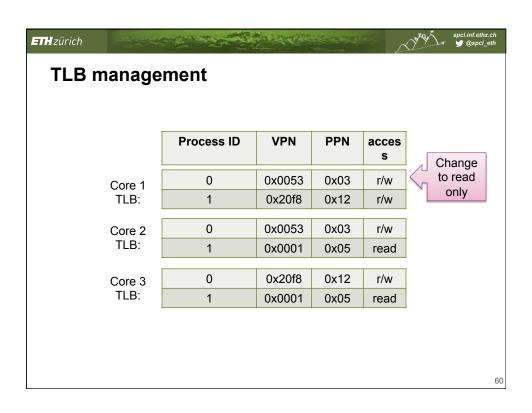

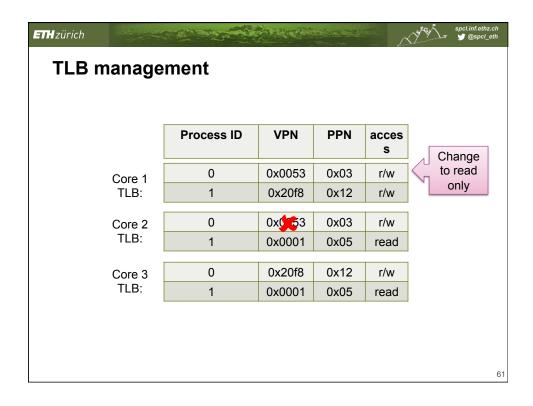

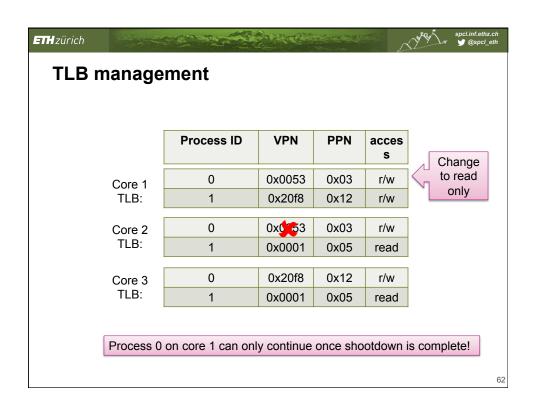

- - Integrate TLB mgmt with cache coherence

- Invalidate TLB entry when PTE memory changes

- Rarely implemented

## Virtual caches

- Required cache flush / invalidate will take care of the TLB

- High context switch cost!

- ⇒ Most processors use physical caches

## 5. Software TLB shootdown

- Most common

- OS on one core notifies all other cores Typically an IPI

- Each core provides local invalidation

## Hardware shootdown instructions

- Broadcast special address access on the bus

- Interpreted as TLB shootdown rather than cache coherence message

- E.g., PowerPC architecture

63