#### **ETH** zürich spei. M

#### **Unix signal handlers**

- Signal handler can be called at any time!

- Executes on the current user stack

- If process is in kernel, may need to retry current system call

- Can also be set to run on a different (alternate) stack

- ⇒ User process is in undefined state when signal delivered

#### EIHzürich spcLinf.ethz.ch y @spcLeth

#### **Implications**

- There is very little you can safely do in a signal handler!

- Can't safely access program global or static variables

- Some system calls are *re-entrant*, and can be called

- Many C library calls cannot (including \_r variants!)

- Can sometimes execute a longjmp if you are careful

- With signal, cannot safely change signal handlers...

- What happens if another signal arrives?

#### Multiple signals

ETH zürich

- If multiple signals of the same type are to be delivered, Unix will discard all but one.

- If signals of different types are to be delivered, Unix will deliver them in any order.

- Serious concurrency problem: How to make sense of this?

#### Signals as upcalls

- Particularly specialized (and complex) form of Upcall

- Kernel RPC to user process

- Other OSes use upcalls much more heavily

- Including Barrelfish

- "Scheduler Activations": dispatch every process using an upcall instead of return

- Very important structuring concept for systems!

#### **Our Small Quiz**

- True or false (raise hand)

- Mutual exclusion on a multicore can be achieved by disabling interrupts

- Test and set can be used to achieve mutual exclusion

- Test and set is more powerful than compare and swap

- The CPU retries load-linked/store conditional instructions after a conflict

- The best spinning time is 2x the context switch time

- Priority inheritance can prevent priority inversion

- The receiver never blocks in asynchronous IPC

- The sender blocks in synchronous IPC if the receiver is not ready

- A pipe file descriptor can be sent to a different process

- Pipes do not guarantee ordering

- Named pipes in Unix behave like files

- A process can catch all signals with handlers

- Signals always trigger actions at the signaled process

- One can implement a user-level tasking library using signals

- Signals of the same type are buffered in the kernel

8

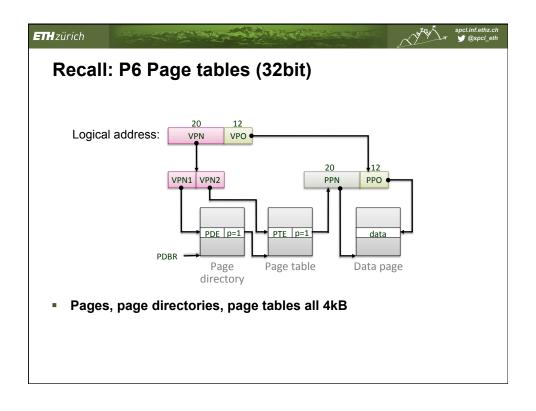

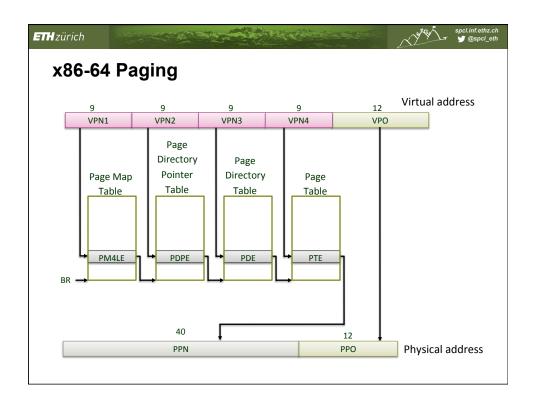

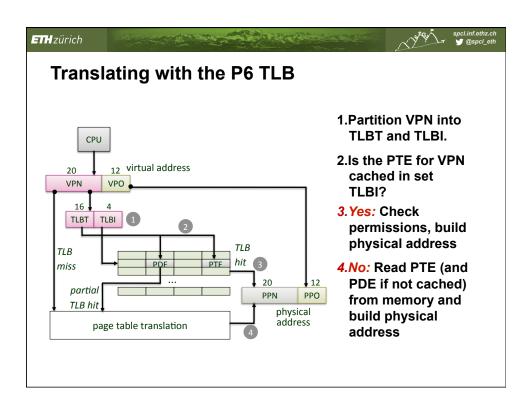

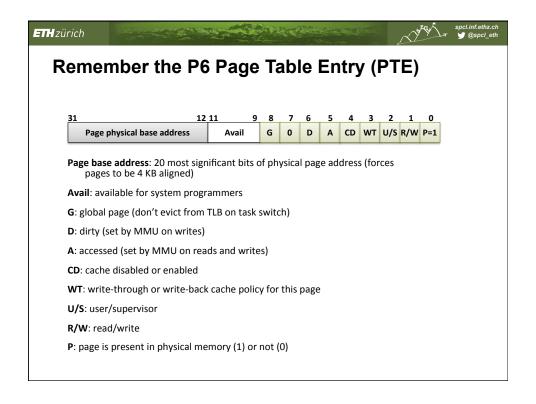

### In CASP last semester we saw:

- Assorted uses for virtual memory

- x86 paging

- Page table format

- Translation process

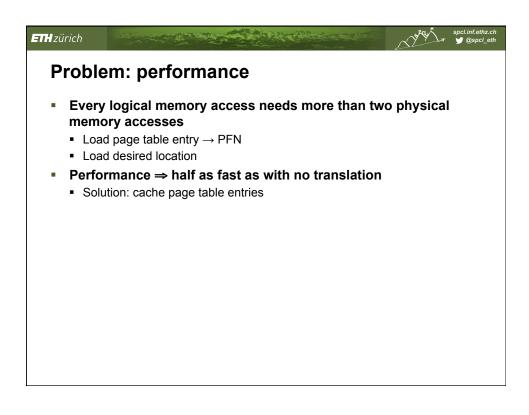

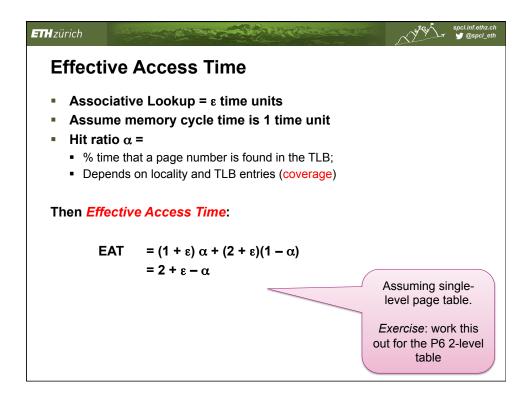

- Translation lookaside buffers (TLBs)

- Interaction with caches

- Performance implications

- For application code, e.g., matrix multiply

#### **ETH** zürich

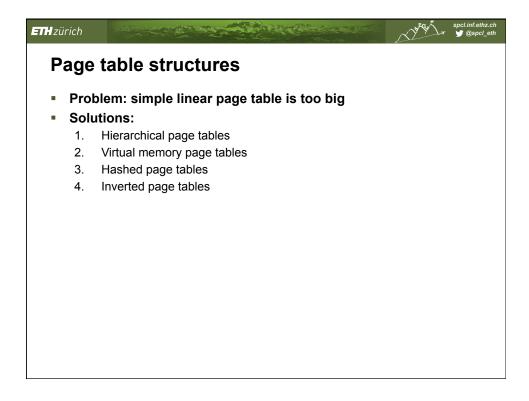

#### What's new this semester?

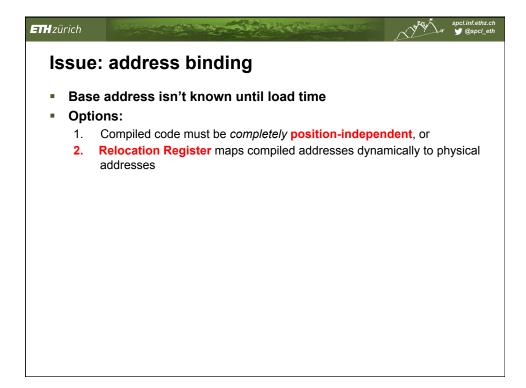

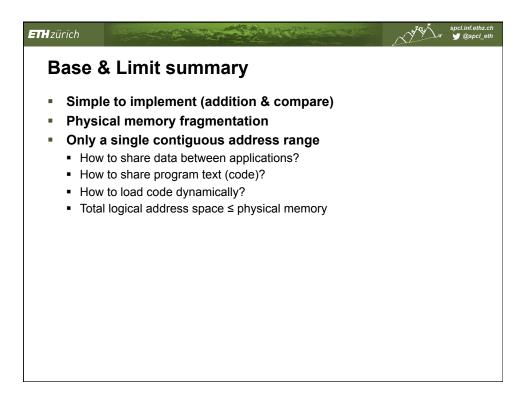

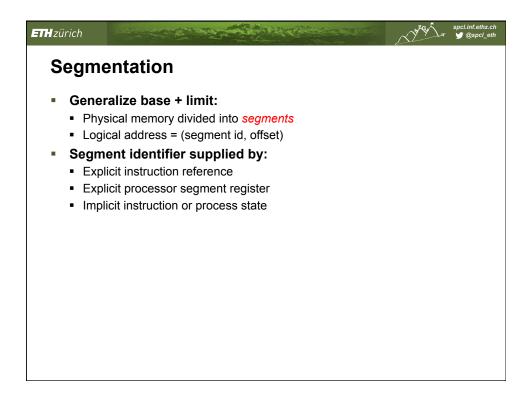

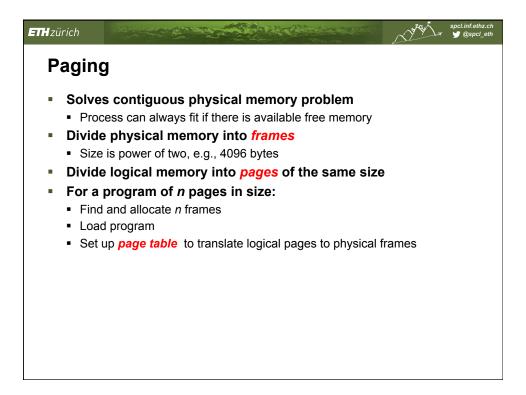

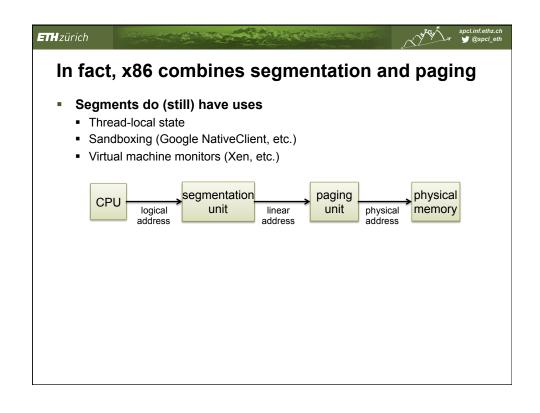

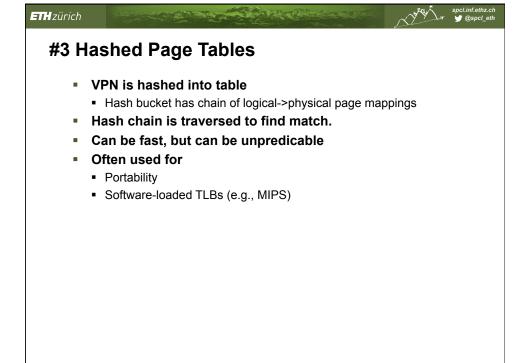

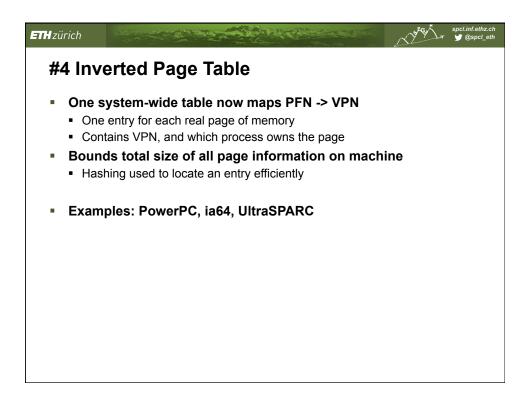

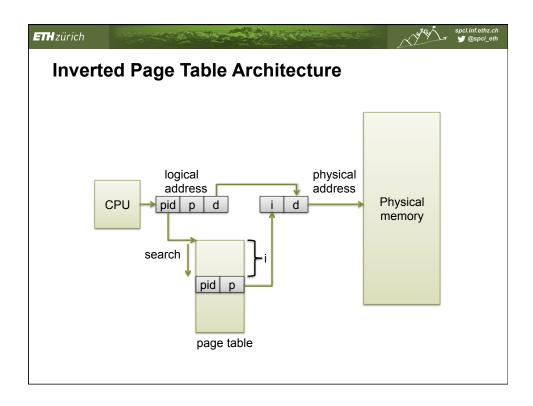

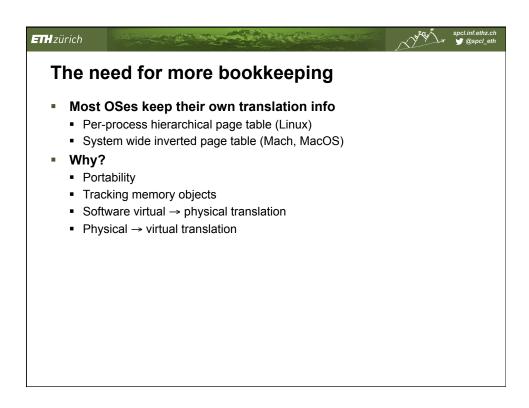

- Wider range of memory management hardware

- Base/limit, segmentation

- Inverted page tables, etc.

- How the OS uses the hardware

- Demand paging and swapping

- Page replacement algorithms

- Frame allocation policies

#### ETH zürich

#### **Terminology**

- Physical address: address as seen by the memory unit

- Virtual or Logical address: address issued by the processor

- Loads

- Stores

- Instruction fetches

- Possible others (e.g., TLB fills)...

#### **Memory management**

- 1. Allocating physical addresses to applications

- 2. Managing the name translation of virtual addresses to physical addresses

- 3. Performing access control on memory access

- Functions 2 & 3 usually involve the hardware Memory Management Unit (MMU)

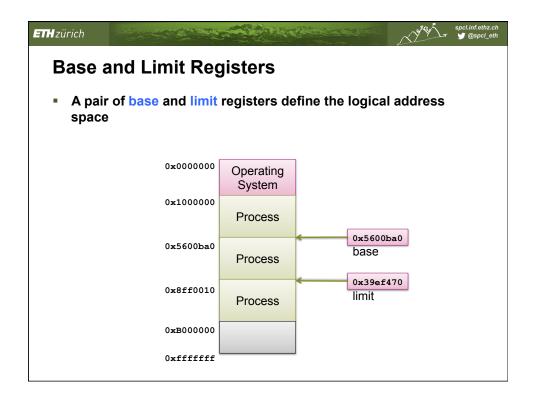

## Contiguous Allocation ■ Main memory usually into two partitions: ■ Resident OS, usually in low memory with interrupt vector ■ User processes in high memory

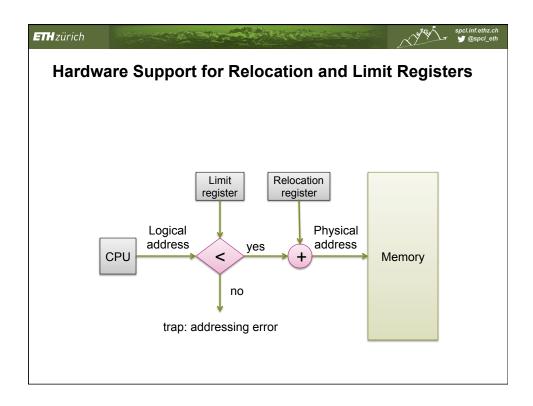

- Relocation registers protect user processes from

- each other

- 2. changing operating-system code and data

- Registers:

- Base register contains value of smallest physical address

- Limit register contains range of logical addresses each logical address must be less than the limit register

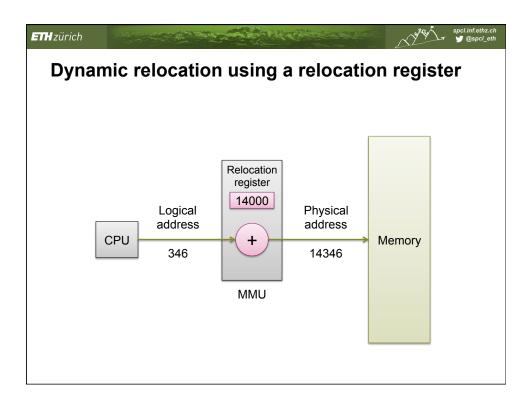

- MMU maps logical address dynamically

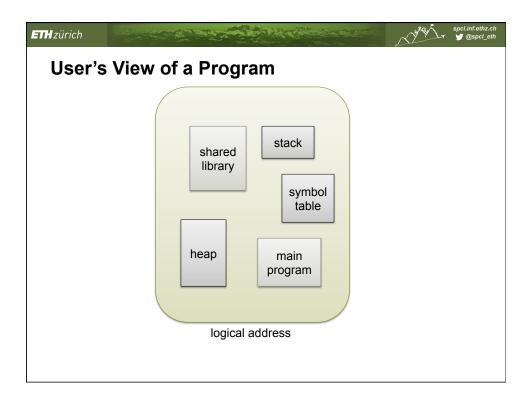

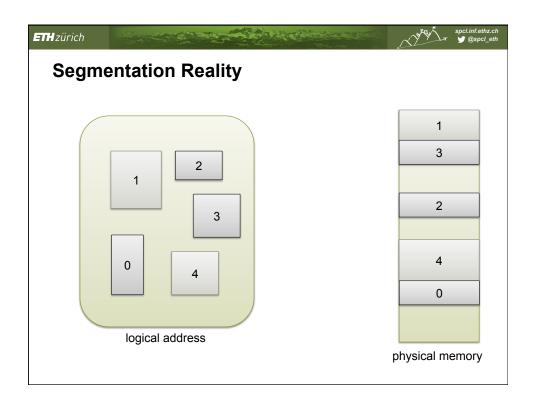

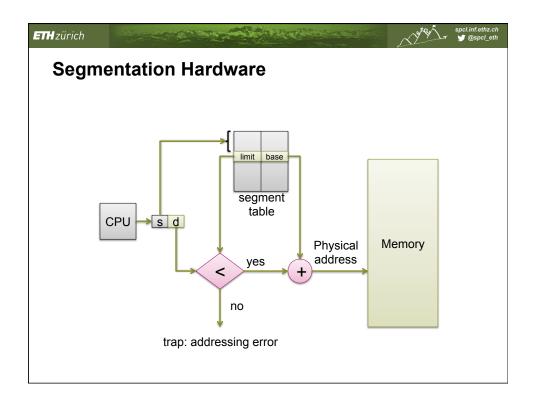

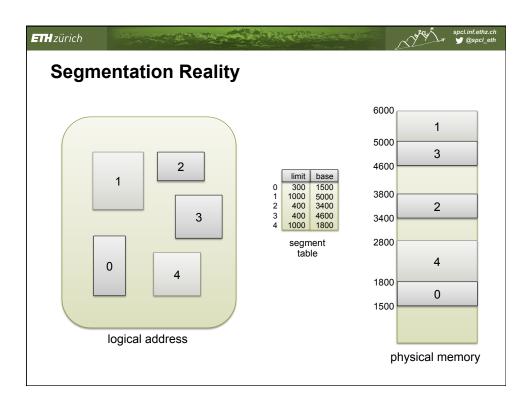

# Segmentation Architecture Segment table – each entry has: base – starting physical address of segment limit – length of the segment Segment-table base register (STBR) Current segment table location in memory Segment-table length register (STLR) Current size of segment table segment number s is legal if s < STLR

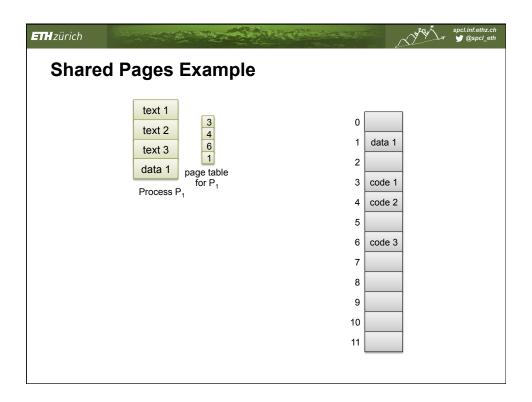

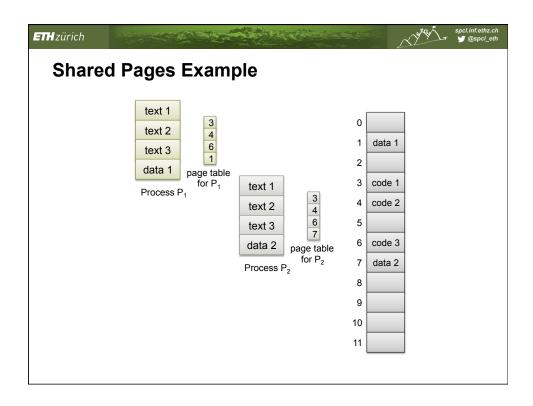

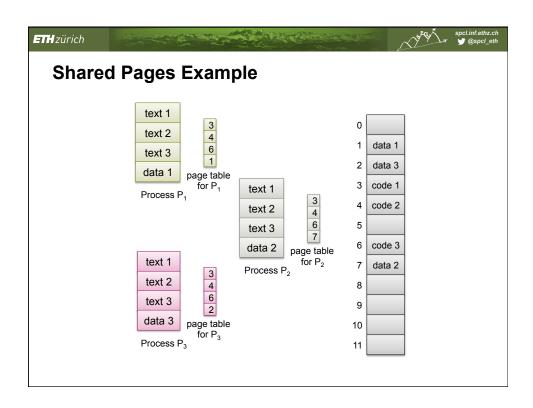

#### **Shared Pages**

ETH zürich

- Shared code

- One copy of read-only code shared among processes

- Shared code appears in same location in the logical address space of all processes

- Data segment is not shared, different for each process

- But still mapped at same address (so code can find it)

- Private code and data

- Allows code to be relocated anywhere in address space

#### ETH zürich

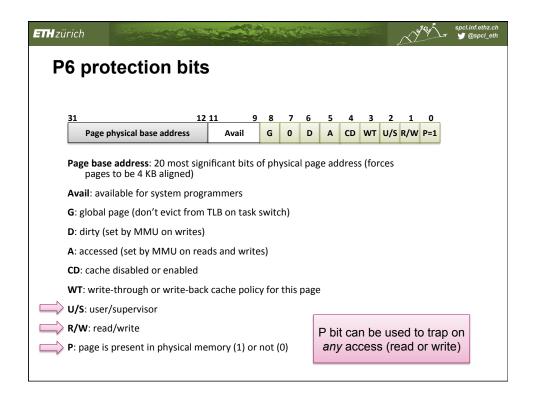

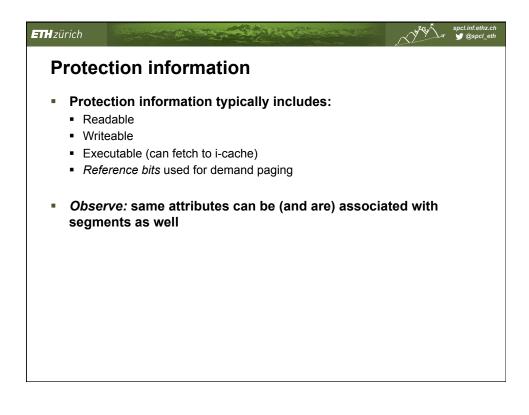

#### **Per-process protection**

- Protection bits are stored in page table

- Plenty of bits available in PTEs

- ⇒ independent of frames themselves

- Different processes can share pages

- Each page can have different protection to different processes

- Many uses! E.g., debugging, communication, copy-on-write, etc.

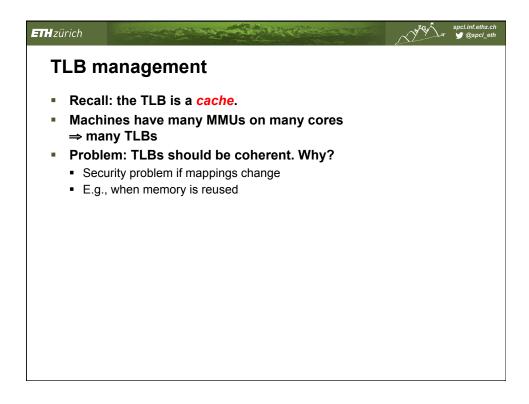

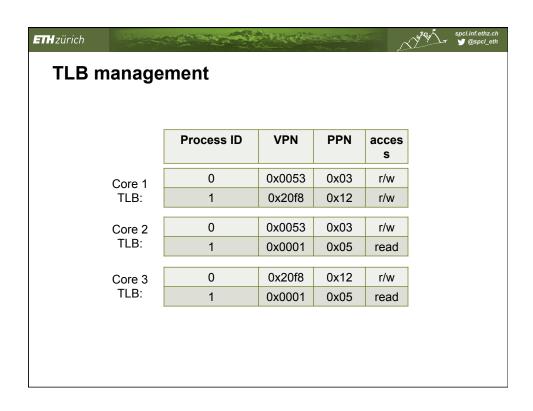

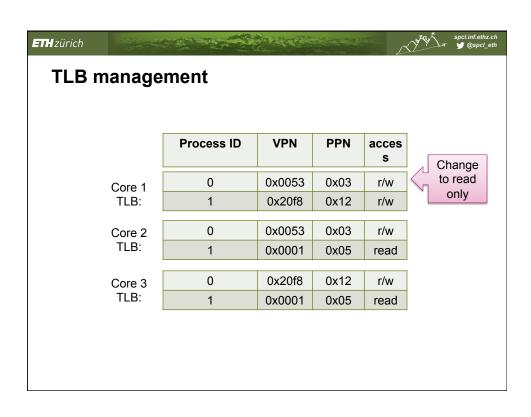

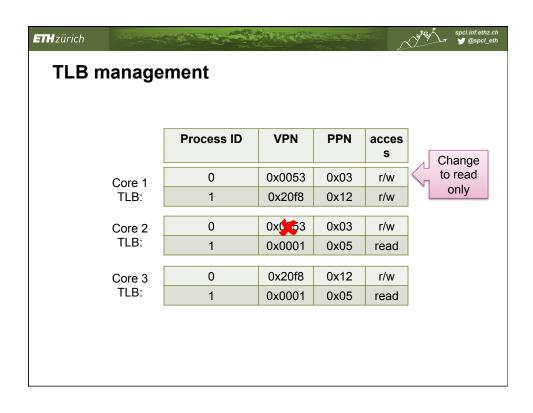

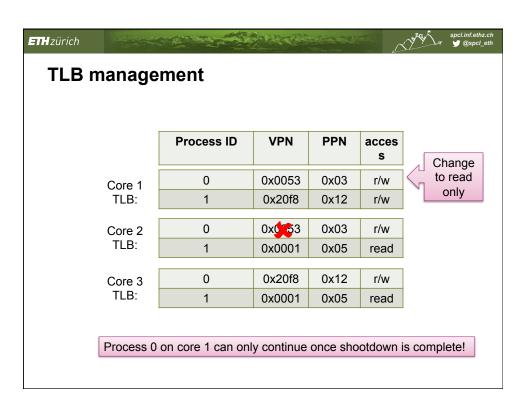

#### **Keeping TLBs consistent**

#### 1. Hardware TLB coherence

- Integrate TLB mgmt with cache coherence

- Invalidate TLB entry when PTE memory changes

- Rarely implemented

#### 2. Virtual caches

- Required cache flush / invalidate will take care of the TLB

- High context switch cost!

- ⇒ Most processors use physical caches

#### 5. Software TLB shootdown

- Most common

- OS on one core notifies all other cores Typically an IPI

- Each core provides local invalidation

#### 6. Hardware shootdown instructions

- Broadcast special address access on the bus

- Interpreted as TLB shootdown rather than cache coherence message

- E.g., PowerPC architecture